TM 11 5895-1096-40

CHAPTER 2

FUNCTIONING OF EQUIPMENT

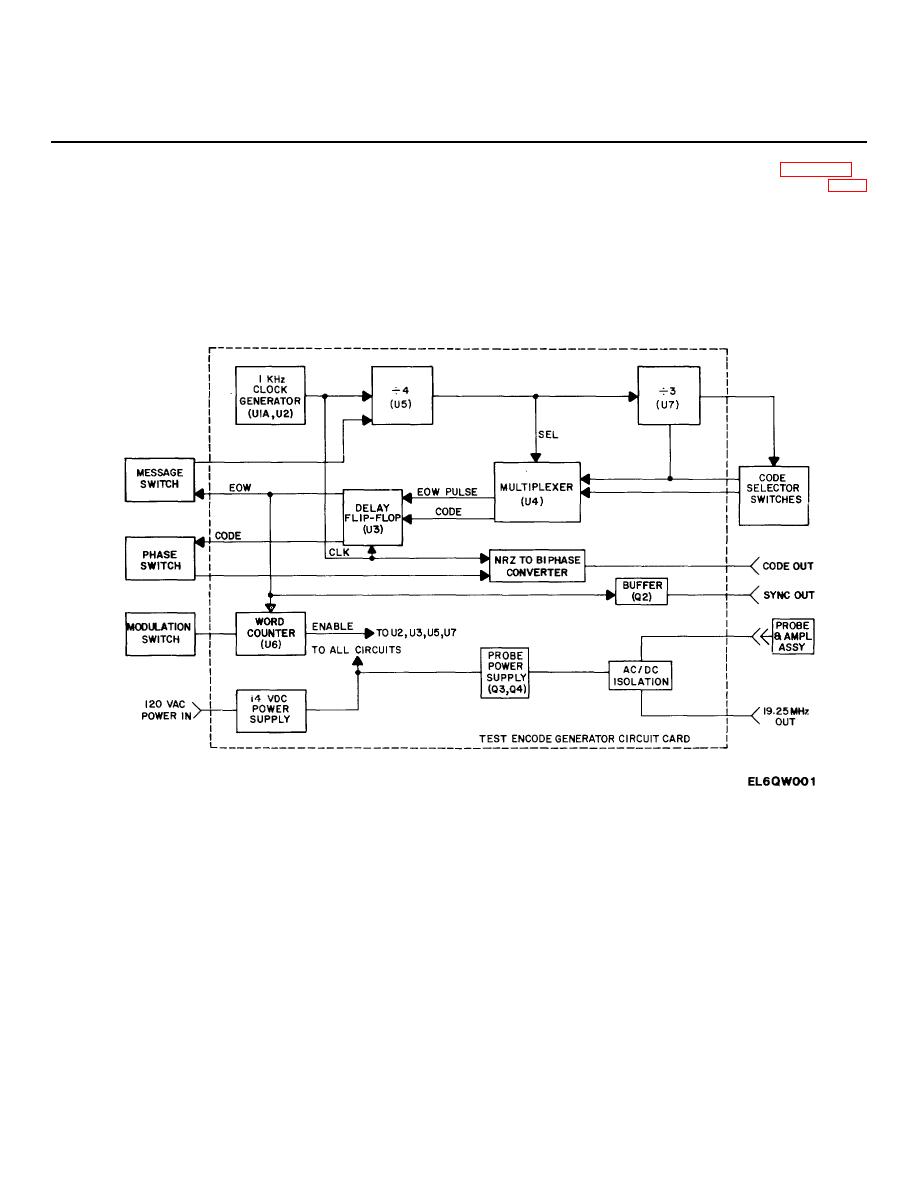

AN/GRA-114 transmitter modulation frequency. Figure 2-1 is

2-1. General

a functional block diagram of the TS-3566/GRA-114. FO-2

The TS-3566/GRA-114 is a highly accurate solid state digital

is a schematic diagram showing all electrical parts and

code generator used to test the AN/GRA-114 receiver

assemblies.

transmitter code reception and transmitter modulation

capabilities. This is accomplished by using the test set code

2-2. Block Diagram Description

output to simulate AN/GRA-114 command transmissions,

(fig.2-1)

while an external probe and amplifier assembly is used to

check the adjustment of the

Figure 2-1. TS-3566/GRA-114 Functional Block Diagram.

a. Message Switch. The message switch, in SO2-STOP

to be generated.

d. 1 KHz Clock Generator. This generator is the heart of

position, applies the end of word (EOW) pulse from the

DELAY IN to the DIVIDE-BY-FOUR IC. In the SO1-START

the encoder circuitry as it produces the I KHz clock signal

position, the circuit remains open.

which establishes all the timing sequences required for code

b. Phase Switch. The phase switch selects which

generation.

e. Divide-by-Four-Counter. This counter produces the

output (Q or Q) from the DELAY IC is provided to the Non-

Return-To-Zero (NRZ) to BIPHASE CONVERTER, thus

binary pulses used to generate the NRZ code. The signal, by

simulating a field wire polarity reversal in actual operation.

operation of J/K flip-flops, is divided into two. One signal

c. Modulation Switch. The modulation switch selects

provides the selector address (SEL) to the multiplexer, and the

other signal is used to drive the DIVIDE-BY-THREE counter.

continuous code or a single burst of code information

2-1